#### Introduction

Terasic, the premier developer of Intel FPGA platforms and Enyx, the leading independent provider of FPGA-enabled, ultra-low latency trading technologies, offering integrated Enyx FPGA IPs for an ultra-low latency, customized development framework on Terasic's DE5a-Net-DDR4 accelerator to address the rapidly-rising demand in today's data and compute-intensive applications.

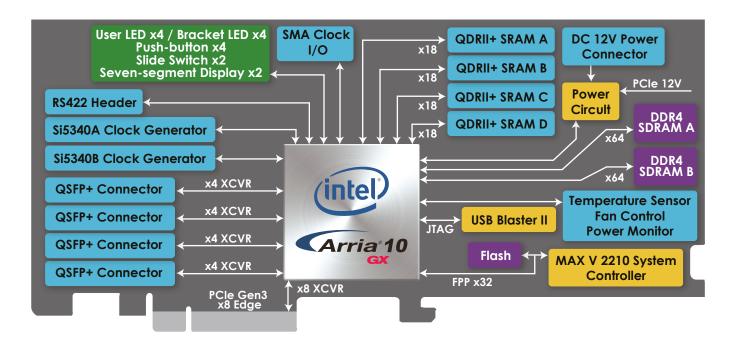

Terasic's DE5a-Net-DDR4 accelerator takes advantage of the powerful Intel Arria 10 FPGA to enable higher speed data processing. The board is armed with 16GB DDR4 memory module, running at over 75 Gbps, up to 7.876 GB/s data transfer via PCIe Gen 3 x8 edge between FPGA and host PC, and 4 on-board QSFP+ connectors. The on-board QDRII memory and DDR4 module can obtain lower application latency and higher application throughput, making it an excellent platform to achieve breakthrough performance in data filtering and algorithmic acceleration.

Enyx develops a powerful customized development framework:

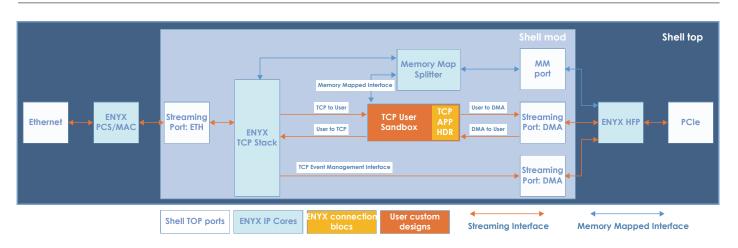

Fenyx Development Framework TCP and DMA Reference Design Architecture of for Terasic's DE5a-Net-DDR4 accelerator. The development framework includes a Sandbox where the user inserts their own custom logic to interface with Enyx IP cores, such as TCP and UDP Stacks, MAC/PCS layers and Enyx's DMA engine (HFP). Packaged with an easy-to-use software API and Linux drivers, the Enyx development framework constitutes the perfect "start-up kit" to reduce time-to-market and jump-start your FPGA-enabled projects.

# **Enyx Development Framework Block Diagram**

## DE5a-Net-DDR4 Block Diagram

### **Major Specs and Interfaces**

Full-height, 3/4-length form-factor package

- High-speed parallel Flash memory

- PCle Gen 3 x8

- With 2x5 timing expansion header for 1pps or other high precision clock inputs

- 2 independent banks of DDR4 SO-DIMM socket, up to 16GB 1066MHz or 8GB 1200MHz for each socket

- 4 Independent 550 MHz QDRII+ SRAMs, 18-bits data bus and 72Mbit for each

- Cooling Option: 1-Slot Air Cooling System: 50mm 6000 RPM fan, Thermal resistance: 1.18 °C/W

#### **Power and Thermals**

- 65W TDP and 85W peak power

- 55 °C TLA

### **Global Solution Partner**

Enyx is a leading, independent provider of FPGA-enabled, ultra-low latency trading and market access technologies. We specialize in high performance market data acquisition and distribution, order execution, and network connectivity management.

We help investment banks, hedge funds, technology service providers, and exchanges streamline their trading infrastructures by providing end-to-end, high performance solutions for latency sensitive trading infrastructures, with global customer service and dependable support.

For more information, please visit enyx.com or visit our LinkedIn page.